CCS Technical Documentation RH-42 Series Transceivers

# System Module

# Contents

|                              | Page No |

|------------------------------|---------|

| Abbreviations                |         |

| Transceiver RH-42 (2220)     |         |

| Introduction                 |         |

| Operational Modes            |         |

| Environmental Specifications |         |

| Normal and extreme voltages  |         |

| Temperature Conditions       |         |

| Engine Module                |         |

| Baseband Module              |         |

| UEM                          |         |

| Introduction to UEM          |         |

| Regulators                   |         |

| RF Interface                 |         |

| Charging Control             |         |

| Digital Interface            |         |

| Audio Codec                  |         |

| UI Drivers                   |         |

| AD Converters                |         |

| UPP                          |         |

| Introduction                 |         |

| Blocks                       |         |

| Flash Memory                 |         |

| Introduction                 |         |

| User Interface Hardware      |         |

| LCD                          |         |

| Introduction                 |         |

|                              |         |

| Interface                    |         |

| Keyboard                     |         |

| Introduction                 |         |

| Power Key                    |         |

| Keys                         |         |

| Lights                       |         |

| Introduction                 |         |

| Interfaces                   |         |

| Technical Information        |         |

| Audio HW                     |         |

| Earpiece                     |         |

| Introduction                 |         |

| Microphone                   | 17      |

| Introduction                 |         |

| Buzzer                       |         |

| Introduction                 |         |

| Battery                      |         |

| Phone Battery                |         |

| Introduction                 |         |

| Interface                    |         |

| Battery Connector            |         |

|                              |         |

| Battery Connector Interface                 | 19 |

|---------------------------------------------|----|

| Accessories Interface                       | 19 |

| System connector                            | 19 |

| Introduction                                | 19 |

| Interface                                   | 19 |

| Technical Information                       |    |

| PPH-1 Handsfree                             |    |

| Introduction                                |    |

| Interface                                   |    |

| Charger IF                                  | 21 |

| Introduction                                |    |

| Interface                                   |    |

| Test Interfaces                             |    |

| Production Test Pattern                     |    |

| Other Test Points                           |    |

| EMC                                         |    |

| General                                     |    |

| BB Component and Control IO Line Protection |    |

| Keyboard lines                              |    |

| C-Cover                                     |    |

| PWB                                         |    |

| LCD                                         |    |

| Microphone                                  |    |

| EARP                                        |    |

| Buzzer                                      |    |

| System Connector Lines                      |    |

| Battery Connector Lines                     |    |

| MBUS and FBUS                               |    |

| Transceiver Interfaces                      |    |

| BB - RF Interface Connections               |    |

| BB - RF Internace Connections               |    |

| UPP Block Signals                           |    |

| Memory Block Interfaces                     |    |

| Audio Interfaces                            |    |

| Key/Display blocks                          |    |

|                                             |    |

| Keyboard Interface<br>Display Interface     |    |

| RF Module                                   |    |

| Requirements                                |    |

| •                                           |    |

| Design                                      |    |

| Software Compensations                      |    |

| Main Technical Characteristics              |    |

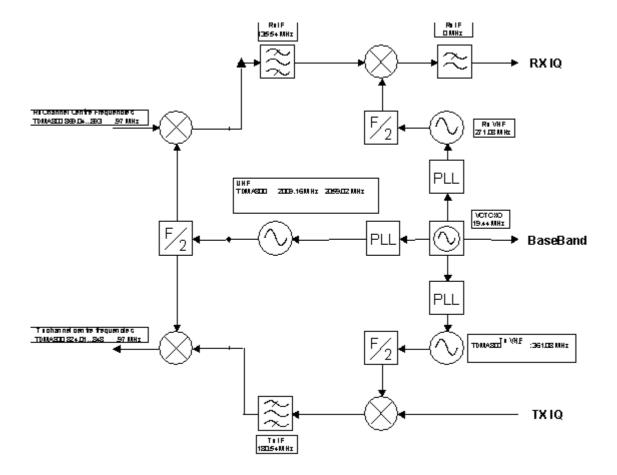

| RF Frequency Plan                           |    |

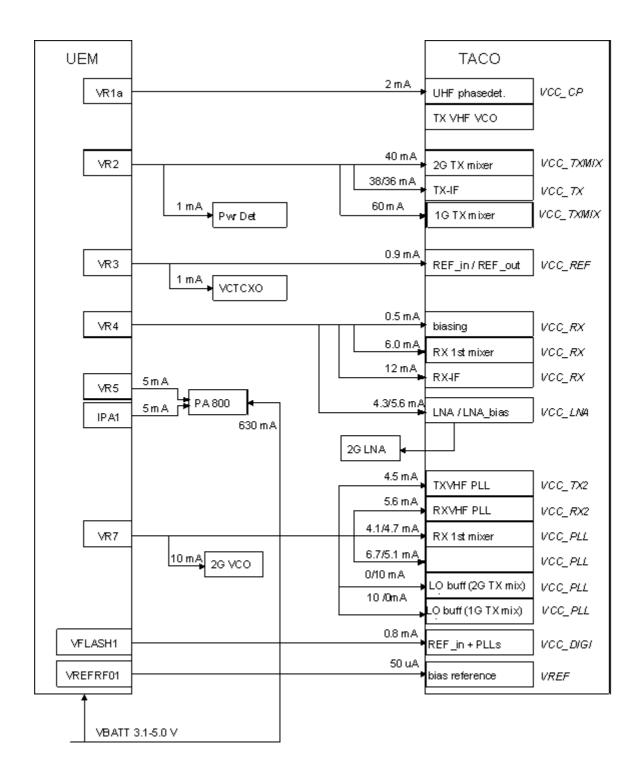

| DC Characteristics                          |    |

| Power Distribution Diagram                  |    |

| Regulators                                  |    |

|                                             |    |

| AMPS/TDMA 800 MHz Front End                 | 46 |

| Frequency Synthesizers | 46 |

|------------------------|----|

| Transmitter            | 47 |

| Common IF              | 47 |

| Cellular Band          | 47 |

| Power Control          | 47 |

| Antenna Circuit        | 48 |

| RF Performance         | 48 |

| Antenna                | 48 |

# Abbreviations

| ACCH   | Analog Control Channel                           |

|--------|--------------------------------------------------|

| A/D    | Analog to Digital conversion                     |

| AMPS   | Advanced Mobile Phone System                     |

| ANSI   | American National Standards Institute            |

| ASIC   | Application Specific Integrated Circuit          |

| AVCH   | Analog Voice Channel                             |

| BB     | Base Band                                        |

| CSD    | Circuit Switched Data                            |

| CSP    | Chipped Scale Package. The same as uBGA.         |

| CTIA   | Cellular Telecommunications Industry Association |

| D/A    | Digital to Analog conversion                     |

| DCCH   | Digital Control Channel                          |

| DSP    | Digital Signal Processing                        |

| DTCH   | Digital Traffic Channel                          |

| EFR    | Enhanced Full Rate (codec)                       |

| FCC    | Federal Communications Commission                |

| IrDA   | Infrared Data Association                        |

| IrMC   | Infrared Mobile Communications                   |

| IrOBEX | IrDA Object Exchange Protocol                    |

| IS     | Interim Standard                                 |

| ISA    | Intelligent Software Architecture                |

| LCD    | Liquid Crystal Display                           |

| LED    | Light Emitting Diode                             |

|        |                                                  |

MO/MTMobile Originated/Mobile Terminated (SMS)

- OOR Out Of Range (mode)

- OTA Over The Air (+ service like Programming etc.)

- PC Personal Computer (PC Suite = PC program for phone memory function support)

- PWB Printed Wired Board

- PWM Pulse Width Modulation

- RF Radio Frequency

- SAR Specific Absorption Rate

- SCF Software Component Factory

- SMD Surface Mount Device

- SMS Short Message Service

- SPR Standard Product Requirement

- TDD Text Device for the Deaf

- TDMA Time Division Multiple Access. Here: US digital cellular system.

- TIA Telecommunications Industry Association

- TTY Teletype

- UEM Universal Energy Management, a Baseband ASIC.

- UPP Universal Phone Processor, a Baseband ASIC.

- VCTCXOVoltage Controlled temperature Compensated Crystal Oscillator

- WAP Wireless Application Protocol (Browser)

# Transceiver RH-42 (2220)

# Introduction

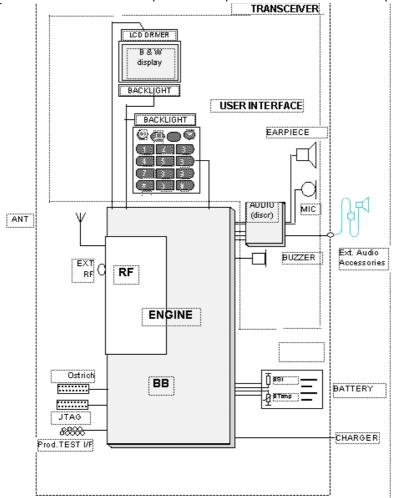

The RH-42 is a single band transceiver unit designed for TDMA800 networks. The transceiver consists of the engine module (ST6S\_11) and the various assembly parts.

The transceiver has a full graphic display and the user interface is based on a Jack style UI with two soft keys. An internal antenna is used in the phone, and there is no connection to an external antenna. The transceiver also has a low leakage tolerant earpiece and an omnidirectional microphone that provides excellent audio quality.

Figure 1: Interconnecting Diagram

# **Operational Modes**

Below is a list of the phone's different operational modes:

- 1 Power Off mode

- 2 Normal Mode (Power controlled by cellular SW, includes various Active and Idle states):

- Analog Modes (800 MHz only):

- •Analog Control Channel, ACCH

- •Analog Voice Channel, AVCH

- Digital Mode (800 MHz):

- •Control Channel, DCCH

- Digital Voice Channel, DTCH (Digital Traffic Channel)

- •Digital Data Channel, DDCH

Both the analog and digital modes have different states controlled by the Cellular SW. Some examples are Idle State (on ACCH), Camping (on DCCH), Scanning, Conversation, NSPS (No Service Power Save, previously OOR = Out of Range).

- 3 Local mode (both Cellular SW and UI SW non active)

- 4 Test mode (Cellular SW active but UI SW non active)

# **Environmental Specifications**

#### Normal and extreme voltages

Voltage range:

- nominal battery voltage: 3.6 V

- maximum battery voltage: 5.0 V

- minimum battery voltage: 3.1 V

# **Temperature Conditions**

Temperature range:

- ambient temperature: -30...+ 60 °C

- PWB temperature: -30...+85 °C

• storage temperature range: -40 to + 85 °C

All of the EIA/TIA-136-270A requirements are not exactly specified over the temperature range. For example, the RX sensitivity requirement is 3dB lower over the -30 - +60 °C range.

# **Engine Module**

# **Baseband Module**

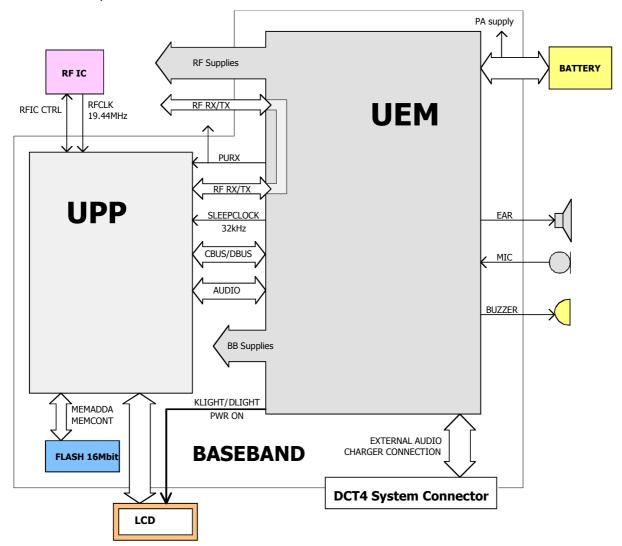

The core part of the transceiver's baseband (see the figure below) consists of two ASICs - the UEM and UPP - and flash memory. The following sections illustrate and explain these parts in detail.

Figure 2: System Block Diagram

# UEM

# Introduction to UEM

UEM is the Universal Energy Management IC for digital hand portable phones. In addition to energy management, it performs all the baseband's mixed-signal functions.

Most UEM pins have 2kV ESD protection, and those signals considered to be more easily exposed to ESD, have 8kV protection within the UEM. These kinds of signals are (1) all audio signals, (2) headset signals, (3) BSI, (4) Btemp, (5) Fbus, and (6) Mbus signals.

# Regulators

The UEM has six regulators for baseband power supplies and seven regulators for RF power supplies. The VR1 regulator has two outputs: (1) VR1a and (2) VR1b. In addition to these, there are two current generators — IPA1 and IPA2 — for biasing purposes.

A bypass capacitor (1uF) is required for each regulator output to ensure stability.

Reference voltages for regulators require external 1uF capacitors. Vref25RF is the reference voltage for the VR2 regulator, Vref25BB is the reference voltage for the VANA, VFLASH1, VFLASH2, VR1 regulators, Vref278 is the reference voltage for the VR3, VR4, VR5, VR6, VR7 regulators, and VrefRF01 is the reference voltage for the VIO, VCORE regulators and for the radio frequency (RF).

| ВВ                            | RF                                | Current     |

|-------------------------------|-----------------------------------|-------------|

| VANA: 2.78Vtyp 80mA max       | VR1a:4.75V 10mA max<br>VR1b:4.75V | IPA1: 0-5mA |

| Vflash1: 2.78Vtyp 70mA max    |                                   | IPA2: 0-5mA |

| Vflash2: 2.78Vtyp<br>40mA max | VR2:2.78V 100mA max               |             |

| VIO: 1.8Vtyp<br>150mA max     | VR4: 2.78V 50mA max               |             |

| Vcore: 1.0-1.8V<br>200mA max  | VR5: 2.78V 50mA max               |             |

|                               | VR6: 2.78V 50mA max               |             |

|                               | VR7: 2.78V 45mA max               |             |

The **VANA** regulator supplies the baseband's (BB) internal and external analog circuitry. It is disabled in the *Sleep* mode.

The **Vflash1** regulator supplies the LCD, the digital parts of the UEM and Taco ASIC. It is enabled during startup and goes into the *low lq-mode* when in the *Sleep* mode.

The **VIO** regulator supplies both the external and internal logic circuitries. It is used by the LCD, flash and UPP. The regulator goes into the *low lq-mode* when in the *Sleep* mode.

The **VCORE** regulator supplies the DSP and the core part of the UPP. The voltage is programmable and the startup default is 1.5V. The regulator goes into the *low lq-mode* when in the *Sleep* mode.

The **VR1** regulator uses two LDOs (VR1A and VR1B) and a charge pump. The charge pump requires one external 1uF capacitor in the Vpump pin and a 220nF flying capacitor between the CCP and CCN pins. In practice, the 220nF flying capacitor is formed by 2 x 100nF capacitors that are parallel to each other. The VR1A regulator is used by the Taco RF ASIC.

The **VR2** regulator is used to supply the (1) external RF parts, (2) lower band up converter, (3) TX power detector module, and (4) Taco. In light load situations, the VR2 regulator can be set to the *low lq-mode*.

The **VR3** regulator supplies the VCTCXO and Taco in the RF. It is always enabled when the UEM is active. When the UEM is in the *Sleep* mode, the VR3 is disabled.

The VR4 regulator supplies the RX frontends (LNA and RX mixers).

The **VR5** regulator supplies the lower band PA. In light load situations, the VR5 regulator can be set to the *low lq-mode*.

The **VR6** regulator supplies the higher band PA and TX amplifier. In light load situations, the VR6 regulator can be set to the *low lq-mode*.

The **VR7** regulator supplies the VCO and Taco. In light load situations, the VR7 regulator can be set to the *low lq-mode*.

The **IPA1** and **IPA2** are programmable current generators. A  $27\Omega/1\%/100$  ppm external resistor is used to improve the accuracy of the output current. The IPA1 is used by the lower PA band and IPA2 is used by the higher PA band.

#### **RF** Interface

The interface between the baseband and the RF section is also handled by the UEM. It provides A/D and D/A conversion of the in-phase and quadrature receive and transmit signal paths. It also provides A/D and D/A conversions of received and transmitted audio signals to and from the UI section. The UEM supplies the analog AFC signal to the RF section, according to the UPP DSP digital control.

#### **Charging Control**

The CHACON block of the UEM asics controls charging. The needed functions for the charging controls are the (1) pwm-controlled battery charging switch, (2) charger-monitoring circuitry, (3) battery voltage monitoring circuitry, and (4) RTC supply circuitry for backup battery charging (Not used in RH-42). In addition to these, external components are needed for EMC protection of the charger input to the baseband module.

#### **Digital Interface**

Data transmission between the UEM and the UPP is implemented using two serial con-

nections, DBUS (programmable clock) for DSP and CBUS (1.0MHz GSM and 1.08MHz TDMA) for MCU. The UEM is a dual voltage circuit: the digital parts are run from 1.8V and the analog parts are run from 2.78V. The Vbat (3,6V) voltage regulators's input is also used.

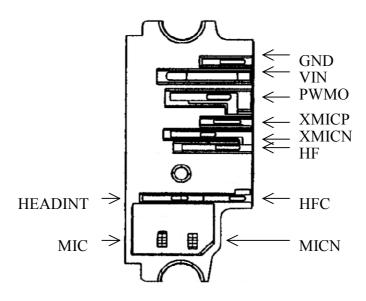

#### Audio Codec

The baseband supports two external microphone input areas and one external earphone output. The input can be taken from an internal microphone, a headset microphone or from an external microphone signal source through a headset connector. The output for the internal earpiece is a dual-ended type output, and the differential output is capable of driving 4Vpp to the earpiece with a 60 dB minimum signal as the total distortion ratio. The input and output signal source selection and gain control is performed inside the UEM Asic, according to the control messages from the UPP.

#### **UI Drivers**

There is a single output driver for the buzzer, display, and keyboard LEDs inside the UEM. These generate PWM square wave for the various devices.

#### **AD Converters**

The UEM is equipped with an 11-channel analog-to-digital converter. Some AD converter channels (LS, KEYB1-2) are not used in RH-42. The AD converters are calibrated in the production line.

# UPP

#### Introduction

RH-42 uses the UPPv4M ASIC. The RAM size is 4M. The processor architecture consists of both the DSP and the MCU processors.

#### Blocks

The UPP is internally partitioned into two main parts: (1) the Brain and (2) the Body.

1 **The Processor and Memory System** (that is, the Processor cores, Mega-cells, internal memories, peripherals and external memory interface) is known as the **Brain**.

The Brain consists of the following blocks: (1) the DSP Subsystem (DSPSS), (2) the MCU Subsystem (MCUSS), (3) the emulation control EMUCtl, (4) the program/ data RAM PDRAM, and (5) the Brain Peripherals-subsystem (BrainPer).

#### 2 The NMP custom cellular logic functions are known as the Body.

The Body contains interfaces and functions needed for interfacing other baseband and RF parts. The body consists of, for example, the following sub-blocks: (1) MFI, (2) SCU, (3) CTSI, (4) RxModem, (5) AccIF, (6) UIF, (7) Coder, (8) BodyIF, and (9) PUP.

# Flash Memory

# Introduction

The RH-42 transceiver uses a 16-Mbit flash as its external memory. The VIO regulator is used as a power supply for normal in-system operation. An accelerated program/erase operation can be obtained by supplying Vpp of 12 volt to the flash device.

The device has two read modes: *asynchronous* and *burst*. The burst read mode is utilized in RH-42, except for the start-up, when the asynchronous read mode is used for a short time.

# **User Interface Hardware**

# LCD

# Introduction

RH-42 uses a black-and-white GD46 84x48 full dot matrix graphical display. The LCD module includes the LCD glass, the LCD COG-driver, an elastomer connector, and a metal frame. The LCD module is included in the lightguide assembly module.

# Interface

The LCD is controlled by the UI SW and the control signals are from the UPP ASIC. The VIO and Vflash1 regulators supply the LCD with power.

The LCD has an internal voltage booster and a booster capacitor is required between Vout and GND.

Pin 3 (Vss9) is the LCD driver's ground and Pin 9 (GND) is used to ground the metal frame.

# Keyboard

# Introduction

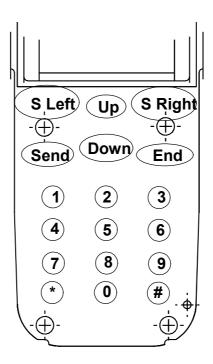

The RH-42 keyboard style follows the Nokia Jack style, without side keys for volume control. The PWR key is located at the top of the phone.

Figure 3: Placement of keys

# Power Key

All signals for the keyboard come from the UPP ASIC, except PWRONX line for the power key signal which is connected directly to the UEM. The pressing of the PWR key grounds the PWRONX line and the UEM generates an interrupt to UOO, which is then recognized as a PWR key press.

# Keys

Other keys are detected so that when a key is pressed down, the metal dome connects one S-line and one R-line of the UPP together and creates an interrupt for the SW. This kind of detection is also known as *metaldome detection*. The matrix of how lines are connected and which lines are used for different keys is described in the following table. The S-line SO and R-line R5 are not used at all.

| Returns /<br>Scans | SO | S1        | S2   | S3   | S4         |

|--------------------|----|-----------|------|------|------------|

| RO                 | NC | NC        | Send | End  | NC         |

| R1                 | NC | Soft left | Up   | Down | Soft right |

| R2                 | NC | 1         | 4    | 7    | *          |

| R3                 | NC | 2         | 5    | 8    | 0          |

| R4                 | NC | 3         | 6    | 9    | #          |

| R5                 | NC | NC        | NC   | NC   | NC         |

# where NC = Not Connected

# NOKIA

**CCS** Technical Documentation

# Lights

# Introduction

RH-42 has has blue LEDs for lighting purposes. The LED type is blue-light emitting and SMD through-hole mounted.

# Interfaces

The display lights are controlled by a Dlight signal from the UEM. The Dlight output is the PWM signal, which is used to control the average current going through the LEDs. When the battery voltage changes, the new PWM value is written onto the PWM register. In this way, the brightness of the lights remains the same with all battery voltages within range. The frequency of the signal is fixed at 128 Hz.

The keyboard lights are controlled by the Klight signal from the UEM. The Klight output is also a PWM signal and is used in the same way as Dlight.

# **Technical Information**

Each LED requires a hole in the PWB, in which the body of the LED locates in hole and terminals are soldered on the component side of the module PWB. The LEDs have a white plastic body around the diode, and this directs the emitted light better to the UI side. The current for the LCD and keyboard lights is limited by the resistor between the Vbatt and LEDs.

# Audio HW

# Earpiece

# Introduction

The speaker is a dynamic one. It is very sensitive and capable of producing relatively high sound pressure also at low frequencies. The speaker capsule and the mechanics around it together make the earpiece.

# Microphone

# Introduction

The microphone is an electret microphone with an omnidirectional polar pattern. It consists of an electrically polarized membrane and a metal electrode which form a capacitor. Air pressure changes (for example, sound) moves the membrane, which causes voltage changes across the capacitor. Because the capacitance is typically 2 pF, a FET buffer is needed inside the microphone capsule for the signal generated by the capacitor. Because of the FET, the microphone needs a bias voltage.

# Buzzer

# Introduction

The operating principle of the buzzer is magnetic. The diaphragm of the buzzer is made

of magnetic material and it is located in a magnetic field created by a permanent magnet. The winding is not attached to the diaphragm, as is the case with the speaker. The winding is located in the magnetic circuit so that it can alter the magnetic field of the permanent magnet, thus changing the magnetic force affecting the diaphragm. The buzzer's useful frequency range is approximately from 2 kHz to 5 kHz.

# Battery

# **Phone Battery**

# Introduction

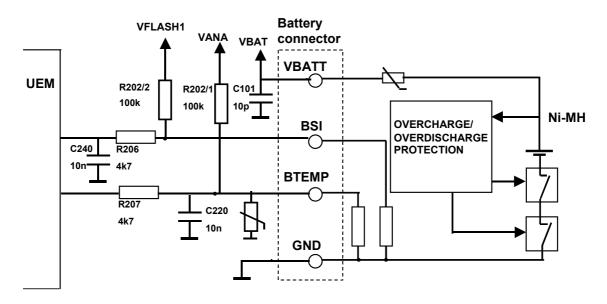

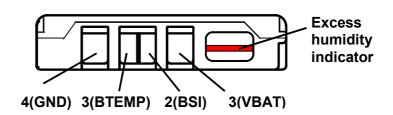

The BMC-3 battery (Ni-MH 900mAh) is be used in the RH-42 transceiver by default. It is also possible to use the BLC-2 (Li-ion 950mA) battery.

# Interface

The battery block contains NTC and BSI resistors for temperature measurement and battery identification. The BSI fixed resistor value indicates the chemistry and default capacity of a battery. The NTC-resistor measures the battery temperature. Temperature and capacity information is needed for charge control. These resistors are connected to BSI and BTEMP pins of the battery connector. The phone has pull-up resistors for these lines so that they can be read by A/D inputs in the phone (see the figure below). Serial resistors in the BSI and BTEMP lines are for ESD protection. Both lines also have spark caps to prevent ESD. There is also a varistor in the BTEMP line for ESD protection.

# Figure 4: Battery Connection Diagram

The batteries have a specific red line, which indicates if the battery has been subjected to excess humidity (red line spreads). The batteries are delivered in the *protection* mode, which gives longer storage time. The voltage seen in the outer terminals is zero (or float-ing), and the battery is activated by connecting the charger. The battery has internal protection for overvoltage and overcurrent.

# **Battery Connector**

RH-42 uses the spring-type battery connector. This makes the phone easier to assemble in production and the connection between the battery and the PWB is more reliable.

# **Battery Connector Interface**

| # | Signal<br>name | Connected        | from – to | Batt. I/<br>O | Signal properti<br>A/Dlevelsfi | Description /<br>Notes |                                    |

|---|----------------|------------------|-----------|---------------|--------------------------------|------------------------|------------------------------------|

| 1 | VBAT           | (+)<br>(batt.)   | VBAT      | I/O           | Vbat                           | 3.0-5.1V               | Battery voltage                    |

| 2 | BSI            | BSI<br>(batt.)   | UEM       | Out           | Ana                            |                        | Battery size<br>indicator          |

| 3 | BTEMP          | BTEMP<br>(batt.) | UEM       | Out           | Ana                            | 40mA/Switch<br>400mA   | Battery temper-<br>ature indicator |

| 4 | GND            | GND              | GND       | GND           | GND                            |                        | Ground                             |

# Accessories Interface

# System connector

# Introduction

RH-42 uses accessories via a system connector.

#### Interface

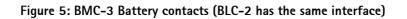

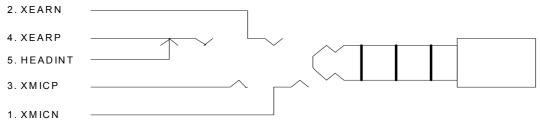

The interface is supported by fully differential 4-wire (XMICN, XMICP, XEARN, and XEARP) accessories. RH-42 supports the HDE-2 inbox headset, HDB-5 Boom headset, HDC-5 headset, LPS-3 loopset, and the PPH-1 car kit.

#### Figure 6: System Connector

An accessory is detected by the HeadInt- line, which is connected to the XEARP inside the system connector. When an accessory is connected, it disconnects XEARP from HEADINT, and the UEM detects it and generates an interrupt (UEMINT) to the MCU. After that, the HOOKINT line is used to determine which accessory is connected. This is done by the voltage divider, which consists of the phone's internal pull-up and accessory-specific pull-down. The voltage generated by this divider is then read by the ad- converter of UEM. The HOOKINT- interrupt is generated by the button in the headset or by the accessory external audio input.

Figure 7: Accessory Detection / External Audio

#### **Technical Information**

ESD protection is made up by (1) spark caps, (2) a buried capacitor (Z152 and Z154-157), and (3)  $\pm$ 8kV inside the UEM The RF and BB noises are prevented by inductors.

# PPH-1 Handsfree

#### Introduction

The PPH-1 handsfree device

- provides the charging and handsfree functionality,

- has a built-in speaker, and

- uses a phone microphone, but also has a connector for the HFM-8 optional external microphone (using HFM-8 mutes phone microphone).

#### Interface

A 4-wire interface is implemented with 2.5 mm diameter round plug/jack which is otherwise like a so-called standard stereo plug, but the innermost contact is split into two.

# Charger IF

#### Introduction

The charger connection is implemented through the system connector. The system connector supports charging with both plug chargers and desktop stand chargers.

There are three signals for charging. The charger GND pin is used for both desktop and plug chargers as well as for charger voltage. The PWM control line, which is needed for 3-wire chargers, is connected directly to the GND in the PWB module, so the RH-42 engine does not provide any PWM control for chargers. Charging controlling is done inside the UEM by switching the UEM's internal charger switch on and off.

#### Interface

The fuse (F100) protects the phone from too-high currents; for example, when broken or pirate chargers are used. L100 protects the engine from RF noises, which may occur in the charging cable. V100 protects the UEM ASIC from reverse-polarity charging voltage and from too-high charging voltages. C106 is also used for ESD and EMC protection. Spark gaps right after the charger plug are used for ESD protection.

# Test Interfaces

# **Production Test Pattern**

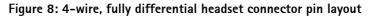

The interface for RH-42 production testing is a 5-pin pad layout in the BB area (see the following figure). The production tester connects to these pads by using spring connectors. The interface includes the MBUS, FBUSRX, FBUSTX, VPP, and GND signals. The pad size is 1.7 mm. The same pads are used also for AS test equipment, such as the module jig and the service cable.

Figure 9: Top View of Production Test Pattern

# **Other Test Points**

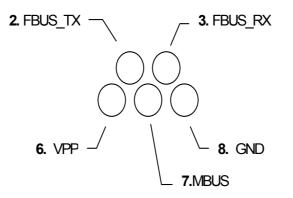

As BB asics and flash memory are CSP components, the visibility of BB signals is very poor. This makes the measuring of most of the BB signals impossible. In order to debug the BB, at least to some level, the most important signals can be accessed from the 0.6 mm test points. The figure below shows the test points located between the UEM and the UPP. There is an opening in the baseband shield to provide access to these pads.

Figure 10: Test points located between UEM and UPP

# EMC

# General

The EMC/ESD performance of RH-42's baseband is improved by using a shield to cover the main components of the BB, such as the UEM, UPP, and Flash. The UEM has internal protection against a  $\pm$ 8kV ESD pulse in most sensitive pins and  $\pm$ 2kV in other pins. The BB shield is soldered to the PWB and it also increases the rigidity of the PWB in the BB area, thus improving the phone's reliability. The shield also improves the thermal dissipation by spreading the heat more widely.

The BB and RF shield are connected together on the PWB and the protective metal deck underneath the battery is grounded to RF shield.

# **BB** Component and Control IO Line Protection

# **Keyboard lines**

ESD protection for keyboard signals is implemented by using separate EMI filter component located between keyboard and UPP. EMI component is a low-pass filter with  $\pm 15$ kV ESD protection. Also the distance from A-cover to PWB is made longer with the spikes in the keymat together with C-cover metallization is protecting keyboard lines.

# C-Cover

The C-cover on the UI side is metallized on the inner surface (partly) and is grounded. All areas in which the plated C-cover touches the PWB surface are grounded and the solder masks are opened.

# PWB

All edges are grounded on both sides of the PWB and the solder mask is opened in these areas. The aim is that any ESD pulse faces the ground area first when entering the phone, for example, between the mechanics covers.

# LCD

ESD protection for LCD is implemented by connecting the metal frame of the LCD into ground. The connection is only on one side, at the top of the LCD, which is not the best solution. The software takes care of the LCD's crashing in case of an ESD pulse.

# Microphone

The microphone's metal cover is connected to the GND and there are spark gaps on the PWB. The microphone is an asymmetrical circuit, which makes it well protected against EMC.

# EARP

The EARP is protected with C-cover metallization and with a plastic-fronted earpiece.

# Buzzer

PWB openings with the C-cover metallization protect the buzzer from ESD.

Page 23

# System Connector Lines

|                               | System Cor | System Connector signals that have EMC protection |       |       |       |         |      |  |  |  |  |  |

|-------------------------------|------------|---------------------------------------------------|-------|-------|-------|---------|------|--|--|--|--|--|

| Protection type               | VIN        | XMIXP                                             | XMICN | XEARP | XEARN | HEADINT | MICP |  |  |  |  |  |

| ferrite bead (600<br>/199MHz) |            | Х                                                 | Х     | Х     | Х     |         | Х    |  |  |  |  |  |

| ferrite bead (420<br>/100MHz) | Х          |                                                   |       |       |       |         |      |  |  |  |  |  |

| spark gaps                    |            | Х                                                 | Х     | Х     | Х     | Х       | Х    |  |  |  |  |  |

| PWB capacitors                |            | Х                                                 | Х     | Х     | Х     | Х       | Х    |  |  |  |  |  |

| RC-circuit                    |            |                                                   | Х     | Х     | Х     | Х       | Х    |  |  |  |  |  |

| capacitor to<br>ground        | Х          | х                                                 | Х     | Х     | Х     |         |      |  |  |  |  |  |

# **Battery Connector Lines**

BSI and BTEMP lines are protected by spark gaps and the RC circuit (4k7 and 10n), in which the resistors are size 0603.

# **MBUS and FBUS**

The opening in the protective metal deck, underneath the battery, is so small that ESD does not get into the MBUS and FBUS lines in the production test pattern.

# **Transceiver Interfaces**

The tables in the following sections illustrate the signals between the various transceiver blocks.

# **BB - RF Interface Connections**

The BB and RF parts are connected together without a physical connector.

All the signal descriptions and properties in the following tables are valid only for active signals, and the signals are not necessarily present all the time.

Note: In the following tables, the nominal signal level of 2.78V is sometimes referred to as 2.7V.

| Rip<br>#    | Signal<br>Name<br>DAMPS,<br>GSM1900 | Connected<br>from to |             |     | BB Signal Properties<br>I/O A/DLevelsFreq./<br>Timing resolution |                         | elsFreq./                       | Description / Notes                                 |  |  |  |  |

|-------------|-------------------------------------|----------------------|-------------|-----|------------------------------------------------------------------|-------------------------|---------------------------------|-----------------------------------------------------|--|--|--|--|

| RFIC        | CNTRL(2:0)                          |                      |             | RF  | RFIC Control Bus from UPP to RFIC(TACO&SAFARI)                   |                         |                                 |                                                     |  |  |  |  |

| 0           | RFBUSCLK                            | UPP                  | RFIC        | In  | Dig                                                              | 0/1.8V                  | 9.72 MHz                        | RF Control serial bus bit clock                     |  |  |  |  |

| 1           | RFBUSDA                             | UPP/RFIC             | RFIC<br>UPP | 1/0 | Dig                                                              | (0: <0.4V<br>1: >1.4 V) |                                 | Bi-directional RF Control serial bus data,          |  |  |  |  |

| 2           | RFBUSEN1X                           | UPP                  | RFIC        | In  | Dig                                                              |                         |                                 | RFIC Chip Sel X                                     |  |  |  |  |

| PUSI        | .(2:0)                              |                      |             | Pov | ver Up                                                           | Reset from              | UEM to RF IC(                   | TACO&SAFARI)                                        |  |  |  |  |

| 0           | PURX                                | UBM                  | RFIC        | Out | Dig                                                              | 0/1.8V                  | 10us                            | Power Up Reset for RF IC                            |  |  |  |  |

|             |                                     |                      |             |     |                                                                  |                         |                                 | SLCLK & SLEEPX not used in RF                       |  |  |  |  |

| GENIO(28:0) |                                     |                      |             |     |                                                                  |                         | ected to RF, se<br>om UPP GENIC | ee also separate collective GENIO(28:0)<br>Os to RF |  |  |  |  |

| 5           | TXP1                                | RFIC                 | UPP         | Out | Dig                                                              | 0/1.8V                  | 10 us                           | SAFARI: Low Band Tx enabled                         |  |  |  |  |

|             |                                     |                      |             |     |                                                                  |                         |                                 | TACO: Low Band&High Band enabled                    |  |  |  |  |

| 6           | TXP2                                | RFIC                 | UPP         | Out | Dig                                                              | 0/1.8V                  |                                 | High Band Tx enabled <b>Only in SAFARI</b> engine.  |  |  |  |  |

| 11          | BANDSEL                             | RFIC                 | UPP         | Out | Dig                                                              | 0/1.8V                  |                                 | Rx Band select. Option for module LNA.              |  |  |  |  |

|             |                                     |                      |             |     |                                                                  |                         |                                 | Only in SAFARI engine.                              |  |  |  |  |

| Rip<br># | Signal<br>Name<br>DAMPS,<br>GSM1900 | Connected<br>from to            |      | _    | BB Signal Properties<br>I/O A/DLevelsFreq./<br>Timing resolution         |                                                                      | elsFreq./    | Description / Notes                                                                                 |  |  |

|----------|-------------------------------------|---------------------------------|------|------|--------------------------------------------------------------------------|----------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------|--|--|

| RFCL     | K (not BUS                          | : -> no rip :                   | #)   |      |                                                                          |                                                                      |              | nal source VCTCXO, buffered (and<br>IC (TACO&SAFARI)                                                |  |  |

|          | RFCLK                               | VCTCX0 -<br>><br>RFIC           | UPP  | In   | Ana                                                                      | 800mVpp<br>typ (FET<br>probed)<br>Bias DC<br>blocked at<br>UPP input | 19.44 MHz    | System Clk from RF to BB,                                                                           |  |  |

|          | RFCIk<br>GND                        | RF                              | UPP  | In   | Ana                                                                      | 0                                                                    |              | System Clock slicer Ref GND, not<br>separated from pwb GND layer                                    |  |  |

| SLOV     | VAD(6:0)                            |                                 |      | Slow | / Spec                                                                   | ed ADC Lines                                                         | from RF bloc | :k                                                                                                  |  |  |

| 5        | PDMID                               | RF Power<br>detection<br>module | UEM  | In   | Ana                                                                      | 0/2.7V dig                                                           | 0/VR2        | Power detection module identification to<br>slow ADC (ch 5, previous VCTCXO Temp)<br>signal to UEM. |  |  |

| 6        | PATEMP                              | RF Power<br>detection<br>module | UEM  | In   | Ana                                                                      | 0.1-2.7V                                                             | -            | Tx PA Temperature signal to UEM, NTC in<br>Power Detection Module                                   |  |  |

|          |                                     |                                 |      |      |                                                                          |                                                                      |              |                                                                                                     |  |  |

| RFCC     | )NV(9:0)                            |                                 | 1    | RF-I | RF- BB differential Analog Signals: Tx I&Q, Rx I&Q and reference voltage |                                                                      |              |                                                                                                     |  |  |

| 0<br>1   | RXIP<br>RXIN                        | RFIC                            | UEM  | In   | Ana                                                                      | 1.4Vpp<br>max. diff.<br>0.5Vpp typ                                   |              | Differential positive/negative in-phase Rx<br>Signal                                                |  |  |

| 2        | RXQP                                | 1                               |      |      |                                                                          | bias                                                                 |              | Diff. Positive/negative quadrature phase Rx                                                         |  |  |

| 3        | RXQN                                | 1                               |      |      |                                                                          | 1.30V                                                                |              | Signal                                                                                              |  |  |

| 4        | TXIP                                | UEM                             | RFIC | Out  | Ana                                                                      | 2.2Vpp                                                               |              | Differential positive/negative in-phase Tx                                                          |  |  |

| 5        | TXIN                                |                                 |      |      |                                                                          | max. diff.<br>0.6VppTvp                                              |              | Signal                                                                                              |  |  |

| 6        | ΤΧΩΡ                                |                                 |      |      |                                                                          | Bias                                                                 |              | Differential positive/negative quadrature                                                           |  |  |

| 7        | ΤΧΩΝ                                |                                 |      |      |                                                                          | 1.30V                                                                |              | phase Tx Signal                                                                                     |  |  |

|          |                                     |                                 |      |      |                                                                          |                                                                      |              |                                                                                                     |  |  |

| 9        | VREFRF01                            | UEM                             | RFIC | Out  | Vtef                                                                     | 1.35 V                                                               |              | RF IC Reference voltage from UEM                                                                    |  |  |

# **NOKIA** CCS Technical Documentation

| Rip<br># | ) Signal<br>Name<br>DAMPS,<br>GSM1900 | Connected<br>from to |        |     | 3B<br>/O                                 | Signal Properties<br>A/DLevelsFreq./<br>Timing resolution |       | A/DLevelsFreq./                        |  | Description / Notes |  |

|----------|---------------------------------------|----------------------|--------|-----|------------------------------------------|-----------------------------------------------------------|-------|----------------------------------------|--|---------------------|--|

| RF       | AUXCONV(2:                            | 0)                   |        | RF_ | RF_BB Analog Control Signals to/from UEM |                                                           |       |                                        |  |                     |  |

|          |                                       |                      |        |     |                                          |                                                           |       |                                        |  |                     |  |

| 1        | TXPWRDET                              | TXP Det.             | UBM    | In  | Ana                                      | 0.1-2.4 V                                                 | 50 us | Tx PWR Detector Signal to UEM          |  |                     |  |

| 2        | AFC                                   | иви                  | VCTCXO | Out | Ana                                      | 0.1-2.4 V                                                 |       | Automatic Frequency Control for VCTCXO |  |                     |  |

|          | 1                                     |                      | 1      |     |                                          | 1                                                         |       |                                        |  |                     |  |

| VRF Globals instead of Bus |               |      |                   |     |        |                  |             | UEM to RF. Current values are of the<br>asured values of RF                                                                     |

|----------------------------|---------------|------|-------------------|-----|--------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

|                            | VR1 A         | UEM  | RFIC              | Out | Vteg   | 4.75∨<br>+-3%    | 10 mA max.  | UEM, charge pump + linear regulator<br>output. Supply for UHF synth phase det                                                   |

|                            | VR1 B         | UEM  | RFIC              | Out | Vteg   | 4.75∨<br>+-3%    | 10 mA max.  | UEM, charge pump + linear regulator<br>output. Only in SAFARI engine, not used<br>in TACO engine.                               |

|                            | VR2           | UEM  | RFDiscr./<br>RFIC | Out | Vteg   | 2.78 V<br>+- 3 % | 100 mA max. | UEM linear regulator. Supply voltage for Tx<br>IQ filter and IQ to Tx IF mixer.                                                 |

|                            | VR3           | UEM  | VCTCXO            | Out | Vteg   | 2.78 V<br>+-3%   | 20 mA max.  | UEM linear regulator. Supply for VCTCXO + RFCLK Buffer in RF IC.                                                                |

|                            | VR4           | UEM  | RFIC              | Out | Vteg   | "                | 50 mA max.  | UEM linear regulator. Power Supply for LNA<br>/ RFIC Rx chain.                                                                  |

|                            | VR5           | UEM  | RFIC              | Out | Vteg   | "                | 50 mA max.  | UEM linear regulator. Power Supply for RF<br>low band PA driver section.                                                        |

|                            | VR6           | UEM  | RFIC              | Out | Vteg   | "                | 50 mA max.  | UEM linear regulator. Power supply for RF<br>high band PA driver section. Only in<br>SAFARI engine, not used in TACO<br>engine. |

|                            | VR7           | UEM  | RFIC,<br>UHF VCO  | Out | Vteg   | "                | 45mA        | UEM linear regulator. Power supply for RF<br>Synths                                                                             |

|                            | IPA1          | UEM  | RF PA             | Out | lout   | 0-5 mA           |             | Settable Bias current for RF PA L-Band                                                                                          |

|                            | IPA2          | UEM  | RFPA              | Out | lout   | 0-5 mA           |             | Settable Bias current for RF PA H-band                                                                                          |

|                            | VFLASH1       | UEM  | RFIC              | Out | lout   | 2.78V            | ~2mA        | UEM linear regulator common for BB.<br>RFIC digital parts and RF to BB digi IF.                                                 |

|                            |               |      |                   |     |        |                  |             |                                                                                                                                 |

| VB                         | VBATT, Global |      |                   |     |        |                  |             |                                                                                                                                 |

|                            | VBATTRF       | Batt | RFPA              | Out | Volatt | 35V              | 01A         | Raw Vbatt for RF PA                                                                                                             |

|                            |               | Conn |                   |     |        | nom 3.6V         | 2A peak     |                                                                                                                                 |

# **BB** Internal Connections

| Rip<br>#                   | Signal<br>Name<br>DAMPS/G<br>SM1900                      |                  | Connected<br>fromto |                                                                   |                                                                                                                                  | A/D-Le                                     | l Properties<br>evelsFreq./<br>1_resolution | Description / Notes                                                                                                                                                                                                             |  |  |  |  |  |

|----------------------------|----------------------------------------------------------|------------------|---------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| REC                        | ONVDA(5:0)                                               | ×                |                     | 1.8V<br>I&Q                                                       | 1.8V digital interface between UPP and UEM. RF Converter CLK, Rx and Tx<br>I&Q data (bit stream signals).                        |                                            |                                             |                                                                                                                                                                                                                                 |  |  |  |  |  |

| 0                          | RFCONVCLK                                                | UPP              | UEM                 | In                                                                | Dig                                                                                                                              | 0/1.8 ∨                                    | 4.86 MHz/<br>Digi<br>3.24 MHz<br>/Ana       | RF Converter Clock                                                                                                                                                                                                              |  |  |  |  |  |

| 1                          | RXID                                                     | UEM              | UPP                 | Out                                                               | 1                                                                                                                                |                                            |                                             | (PDM) RxI Data                                                                                                                                                                                                                  |  |  |  |  |  |

| 2                          | RXQD                                                     | 1                |                     |                                                                   |                                                                                                                                  |                                            |                                             | (PDM) RxQ Data                                                                                                                                                                                                                  |  |  |  |  |  |

| 3                          | TXID                                                     | UPP              | UEM                 | In                                                                | 1                                                                                                                                |                                            |                                             | (PDM) Txl Data                                                                                                                                                                                                                  |  |  |  |  |  |

| 4                          | TXQD                                                     | 1                |                     |                                                                   |                                                                                                                                  |                                            |                                             | (PDM) TxQ Data                                                                                                                                                                                                                  |  |  |  |  |  |

| 5                          | AUXDA                                                    | UPP              | UEM                 | In                                                                | 1                                                                                                                                |                                            |                                             | Auxiliary DAC Data                                                                                                                                                                                                              |  |  |  |  |  |

|                            |                                                          |                  |                     |                                                                   |                                                                                                                                  |                                            | •                                           |                                                                                                                                                                                                                                 |  |  |  |  |  |

| REC                        | ONVCTRL(2                                                | :0)*             |                     | 1.8V<br>IF bi                                                     | 1.8V digital interface between UPP (DSP) and UEM, RF Converter and UEM RF<br>IF <u>bidirectional</u> serial Control Bus, "DBUS", |                                            |                                             |                                                                                                                                                                                                                                 |  |  |  |  |  |

| 0                          | DBUSCLK                                                  | UPP              | UEM                 | In                                                                | Dig                                                                                                                              | 0/1.8 V                                    | 9.72MHz                                     | Clock for Fast Control to UEM                                                                                                                                                                                                   |  |  |  |  |  |

| 1                          | DBUSDA                                                   | 1                |                     | In/Qu                                                             | 1                                                                                                                                |                                            |                                             | Fast Control Data to/from UEM                                                                                                                                                                                                   |  |  |  |  |  |

| 2                          | DBUSENX                                                  |                  |                     | In                                                                | ]                                                                                                                                |                                            |                                             | Fast Control Data Load /Enable_to UEM                                                                                                                                                                                           |  |  |  |  |  |

| AUD                        | UEMCTRL(S                                                | ):O)*            |                     | 1.8V<br>"CBI                                                      |                                                                                                                                  | al interface                               | between UPP                                 | (MCU) and UEM, <u>Bidirectional</u> Control Bus                                                                                                                                                                                 |  |  |  |  |  |

| 0                          | UEMINT                                                   | UEM              | UPP                 | Out                                                               | Dig                                                                                                                              | 0/1.8 V                                    |                                             | UEM Interrupt                                                                                                                                                                                                                   |  |  |  |  |  |

| 1                          | CBUSCLK                                                  |                  |                     |                                                                   |                                                                                                                                  |                                            |                                             |                                                                                                                                                                                                                                 |  |  |  |  |  |

|                            |                                                          | UPP              | UEM                 | In                                                                |                                                                                                                                  |                                            | 1.08 MHz                                    | Clock for Control/Audio Convertors in UEM                                                                                                                                                                                       |  |  |  |  |  |

| 2                          | CBUSDA                                                   |                  | UEM                 | In<br>In/Qu                                                       |                                                                                                                                  |                                            | 1.08 MHz<br>1.08Mbit/s                      | Clock for Control/Audio Convertors in UEM<br>Control Data                                                                                                                                                                       |  |  |  |  |  |

| 2<br>3                     | CBUSDA<br>CBUSENX                                        | UPP              | UEM                 |                                                                   |                                                                                                                                  |                                            |                                             |                                                                                                                                                                                                                                 |  |  |  |  |  |

| 3                          | 1                                                        |                  | UEM                 | In/Qu<br>In<br>1.8V                                               |                                                                                                                                  | al audio inte<br>y CBUSCLI                 | 1.08Mbit/s<br>erface betweer                | Control Data                                                                                                                                                                                                                    |  |  |  |  |  |

| 3                          | CBUSENX                                                  |                  | UEM                 | In/Qu<br>In<br>1.8V                                               |                                                                                                                                  |                                            | 1.08Mbit/s<br>erface betweer                | Control Data<br>Control Data Load Signal                                                                                                                                                                                        |  |  |  |  |  |

| 3<br>AUD                   | CBUSENX                                                  | )*               |                     | In/Qu<br>In<br>1.8V<br>cloc                                       | keď by                                                                                                                           | Y CBUSCLI                                  | 1.08Mbit/s<br>erface between<br>K           | Control Data<br>Control Data Load Signal<br>UPP and UEM audio codec, PDM data<br>PDM Data for Downlink Audio, clocked by                                                                                                        |  |  |  |  |  |

| 3<br>AUD<br>O              | CBUSENX                                                  | )*<br>UPP        | UEM                 | In/Qu<br>In<br>1.8V<br>cloc                                       | keď by                                                                                                                           | Y CBUSCLI                                  | 1.08Mbit/s<br>erface between<br>K           | Control Data<br>Control Data Load Signal<br>UPP and UEM audio codec, PDM data<br>PDM Data for Downlink Audio, clocked by<br>CBUSCLK<br>PDM Data for uplink Audio, clocked by                                                    |  |  |  |  |  |

| 3<br>AUD<br>0<br>1         | CBUSENX                                                  | )*<br>UPP        | UEM                 | In Qu<br>In Qu<br>In<br>1.8V<br>cloc<br>In<br>Out                 | Dig                                                                                                                              | y CBUSCLI<br>0/1.8 ∨<br>al SIM signa       | 1.08Mbit/s                                  | Control Data<br>Control Data Load Signal<br>UPP and UEM audio codec, PDM data<br>PDM Data for Downlink Audio, clocked by<br>CBUSCLK<br>PDM Data for uplink Audio, clocked by                                                    |  |  |  |  |  |

| 3<br>AUD<br>0<br>1         | CBUSENX<br>IODATA(1:0<br>EARDATA<br>MICDATA              | )*<br>UPP        | UEM                 | In Qu<br>In Qu<br>In<br>1.8V<br>cloc<br>In<br>Out                 | digitz                                                                                                                           | y CBUSCLI<br>0/1.8 ∨<br>al SIM signa       | 1.08Mbit/s                                  | Control Data<br>Control Data Load Signal<br>UPP and UEM audio codec, PDM data<br>PDM Data for Downlink Audio, clocked by<br>CBUSCLK<br>PDM Data for uplink Audio, clocked by<br>CBUSCLK                                         |  |  |  |  |  |

| 3<br>AUD<br>0<br>1<br>ISIM | CBUSENX<br>IODATA(1:0<br>EARDATA<br>MICDATA<br>IIE(2:0)* | )*<br>UPP<br>UEM | UEM                 | In/Qu<br>In/Qu<br>In<br>1.8V<br>Cloc<br>In<br>Out<br>1.8V<br>1X/N | keď by<br>Dig<br>digitz<br>KW-1                                                                                                  | y CBUSCLI<br>0/1.8 ∨<br>al SIM signa<br>CX | 1.08Mbit/s                                  | Control Data<br>Control Data Load Signal<br>DUPP and UEM audio codec, PDM data<br>PDM Data for Downlink Audio, clocked by<br>CBUSCLK<br>PDM Data for uplink Audio, clocked by<br>CBUSCLK<br>PP and UEM, wired, not used in NKW- |  |  |  |  |  |

1

| Rip<br>#      | Signal<br>Name<br>DAMPS,<br>GSM1900   | fron | ected<br>1 to |              | UEM Signal Properties<br>I/O A/DLevelsFreq<br>Timing resolution |                | /elsFreq./                  | Description / Notes                     |

|---------------|---------------------------------------|------|---------------|--------------|-----------------------------------------------------------------|----------------|-----------------------------|-----------------------------------------|

| PUSI          | L(2:0)*                               |      |               | Pow          | er-Up                                                           | & Sleep Co     | ntrol lines                 |                                         |

| 0             | · · · · · · · · · · · · · · · · · · · |      | UPP<br>RFIC   | Out          | Dig                                                             | 0/1.8 V        |                             | Power Up Reset, 0 at reset              |

| 1             | SLEEPX                                | UPP  | UEM           | In           | ]                                                               |                |                             | Power Save Functions, active low        |

| 2             | SLEEPCLK                              | UEM  | UPP           | Out          | ]                                                               |                | 32.768 kHz                  | 32 kHz Sleep Clock                      |

| IACCDIF(5:0)* |                                       |      |               | BB II<br>UEM |                                                                 | al 1.8V Digit: | al Accessory B              | uses between UPP and 2.7V level shifter |

| 0             | IRTX                                  | UPP  | UEM           |              |                                                                 | 0/1.8 V        | 1.152 Mbit/s                |                                         |

| Ŭ             |                                       | 0    | 02            | <sup>0</sup> |                                                                 |                | max                         | 1/NKW-1C.                               |

| 1             | IRRX                                  | UEM  | UPP           | In           |                                                                 |                |                             | Infrared Receive                        |

| 2             | MBUSTX                                | UPP  | UEM           | In           | Dig                                                             | 0/1.8 V        | 9k6 b/s                     | MBUS Transmit                           |

| 3             | MBUSRX                                | UEM  | UPP           | Out          |                                                                 |                | 9k6 b/s                     | MBUS Receive / FDL C/k                  |

|               |                                       |      |               |              |                                                                 |                | <7Mb/s                      |                                         |

| 4             | FBUSTXI                               | UPP  | UEM           | In           | Dig                                                             | 0/1.8 V        | <115kb/s                    | FBUS Transmit / FDL Tx                  |

|               |                                       |      |               |              |                                                                 |                | <1Mb/s                      |                                         |

| 5             | FBUSRXI                               | UEM  | UPP           | Out          |                                                                 |                | <115kb/s<br><7 <i>Mb</i> ∕s | FBUS Receive I FDL Rx                   |

| SLO | WAD(6:0)* |                     |      | SLov | w Spe                                                       | ed ADC Lines             | UEM external                                                                                        |  |  |  |  |

|-----|-----------|---------------------|------|------|-------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| 0   | BSI       | BATTE               | UEM  | In   | Ana                                                         | 0-2.7V                   | Battery Size Indicator/FDL init                                                                     |  |  |  |  |

| 1   | BTEMP     | RY                  |      |      |                                                             |                          | Battery Temperature                                                                                 |  |  |  |  |

| 5   | PDMid     | RF<br>PDMod         | UEM  | In   | Ana                                                         | 0-2.7V                   | Power detection module identification to<br>slow ADC (ch 5, previous VCTCXO Temp)<br>signal to UEM. |  |  |  |  |

| 6   | PATEMP    | RF;<br>PDMod<br>NTC |      |      |                                                             |                          | Tx PA Temperature, Measured from Power<br>Detection Module                                          |  |  |  |  |

|     |           |                     |      |      |                                                             |                          |                                                                                                     |  |  |  |  |

| RFC | ONV(9:0)* |                     |      | RF-E | RF- BB Analog Signals: Tx I&Q, Rx I&Q and ref (TACO&SAFARI) |                          |                                                                                                     |  |  |  |  |

| 0   | RXIP      | RFIC                | UEM  | In   | Ana                                                         | 1.4Vpp                   | Differential positive/negative in-phase Rx                                                          |  |  |  |  |

| 1   | RXIN      |                     |      |      |                                                             | max. diff.<br>0.5Vpp typ | Signal                                                                                              |  |  |  |  |

| 2   | RXQP      | 1                   |      |      |                                                             | bias                     | Diff. Positive/negative quadrature phase Rx                                                         |  |  |  |  |

| 3   | RXQN      | 1                   |      |      |                                                             | 1.30V                    | Signal                                                                                              |  |  |  |  |

| 4   | TXIP      | UEM                 | RFIC | Out  | Ana                                                         | 2.2Vpp                   | Differential positive/negative in-phase Tx                                                          |  |  |  |  |

| 5   | TXIN      | 1                   |      |      |                                                             | max. diff.<br>0.6VppTyp  | Signal                                                                                              |  |  |  |  |

| 6   | ΤΧΩΡ      | 1                   |      |      |                                                             | Bias                     | Differential positive/negative quadrature                                                           |  |  |  |  |

| 7   | ΤΧΩΝ      | 1                   |      |      |                                                             | 1.30V                    | phase Tx Signal                                                                                     |  |  |  |  |

|     |           |                     |      |      |                                                             |                          |                                                                                                     |  |  |  |  |

| 9   | VREFRF01  | UEM                 | RFIC | Out  | Vtef                                                        | 1.35 V                   | RF IC Reference voltage from UEM                                                                    |  |  |  |  |